凑数

凑数

凑数

凑数

在微型机系统中,I/O设备通过()与主板的系统总线相连接。

A.DMA控制器

B.设备控制器

C.中断控制器

D.I/O端口

解析

B

IO设备不可能直接与主板总线相连,它总是通过设备控制器来相连的。

下列关于IO指令的说法中,错误的是()。

A.I/O指令是CPU系统指令的一部分

B.IO指令是机器指令的一类

C. IO指令反映CPU和IO设备交换信息的特点

D.I/O指令的格式和通用指令格式相同

解析

2.D

IO指令是指令系统的一部分,是机器指令的一类,但其为了反映与IO设备交互的特点格式和其他通用指令相比有所 $\color{green}{\text{不同}}$ 。

以下关于通道程序的叙述中,正确的是()。

A.通道程序存放在主存中

B.通道程序存放在通道中

C.通道程序是由CPU执行的

D、通道程序可以在任何环境下执行I/O操作

解析

3.A

通道程序存放在 $\color{green}{\text{主存}}$ 而非通道中,由通道从主存中取出并执行。 $\color{green}{\text{通道程序}}$ 由 $\color{green}{\text{通道}}$ 执行,且 $\color{red}{\text{只能}}$ 在具有通道的IO系统中执行。

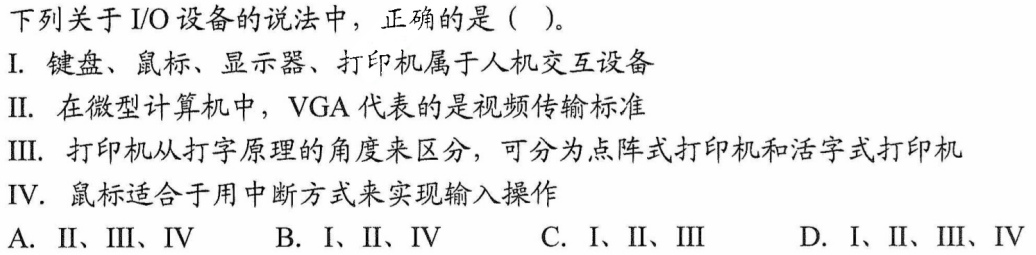

按照打字原理来划分

图片详情

解析

图片详情

- $\color{red}{\text{原理}}$ :可分为 $\color{green}{\text{击打式}}$ 和 $\color{green}{\text{非击打式}}$ 两种

- 能否打出 $\color{red}{\text{汉字}}$ 来分,可分为 $\color{green}{\text{点阵式打印机}}$ 和 $\color{green}{\text{活字式打印机}}$

一台字符显示器的VRAM中存放的是()。

A.显示字符的ASCII码

B.BCD码

C.字模

D.汉字内码

解析

$\color{green}{\text{A}}$

在字符显示器的 $\color{green}{\text{VRAM}}$ 中存放 $\color{green}{\text{ASCII码}}$ 用以显示字符。

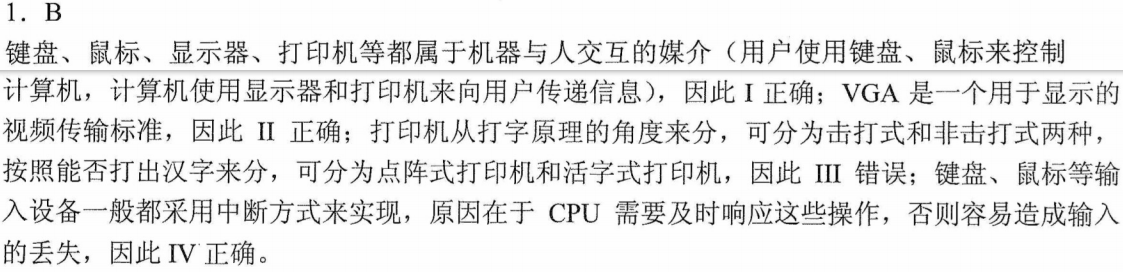

CRT的分辨率为1024×1024像素,像素的颜色数为256,则刷新存储器的每单元字长为(),总容量为()。

A. 8B,256MB

B. 8bit,1MB

C. 8bit,256KB

D.8B,32MB

解析

图片详情

【2013统考真题】某磁盘的转速为10000 转/分,平均寻道时间是6ms,磁盘传输速率是20MB/s,磁盘控制器延迟为0.2ms,读取一个4KB的扇区所需的平均时间约为()。

A. 9ms

B.9.4ms

C. 12ms

D. 12.4ms

解析

8.B

磁盘转速是10000 转/分,转一圈的时间为6ms,因此平均查询扇区的时间为3ms,平均寻道时间为6ms,读取4KB扇区信息的时间为0.2ms,信息延迟的时间为4KB/(20MB/s)= 0.2ms,总时间为3+6+0.2+0.2= 9.4ms。

- 转速是用来求查询扇区所需要的时间( $\color{green}{\text{旋转延迟时间}}$ )

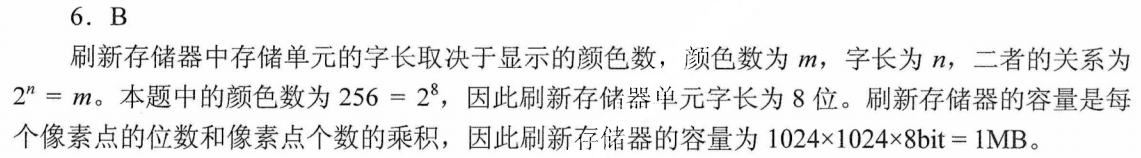

【2015统考真题】若磁盘转速为7200转/分,平均寻道时间为8ms,每个磁道包含1000个扇区,则访问一个扇区的平均存取时间大约是().

A. 8.1ms

B.12.2ms

C.16.3ms

D.20.5ms

解析

图片详情

- 注意要用平均延迟时间来当旋转延迟时间

【2019统考真题】下列关于磁盘存储器的叙述中,错误的是()

A.磁盘的格式化容量比非格式化容量小

B.扇区中包含数据、地址和校验等信息

C.磁盘存储器的最小读写单位为1字节

D.磁盘存储器由磁盘控制器、磁盘驱动器和盘片组成

解析

12.C

磁盘存储器的最小读写单位为一个扇区,即磁盘 $\color{green}{\text{按块存取}}$ ,C错误。磁盘存储数据之前需要进行格式化,将磁盘分成扇区,并写入信息,因此磁盘的格式化容量比非格式化容量小,A正确。磁盘扇区中包含数据、地址和校验等信息,B正确。磁盘存储器由磁盘控制器、磁盘驱动器和盘片组成,D正确。

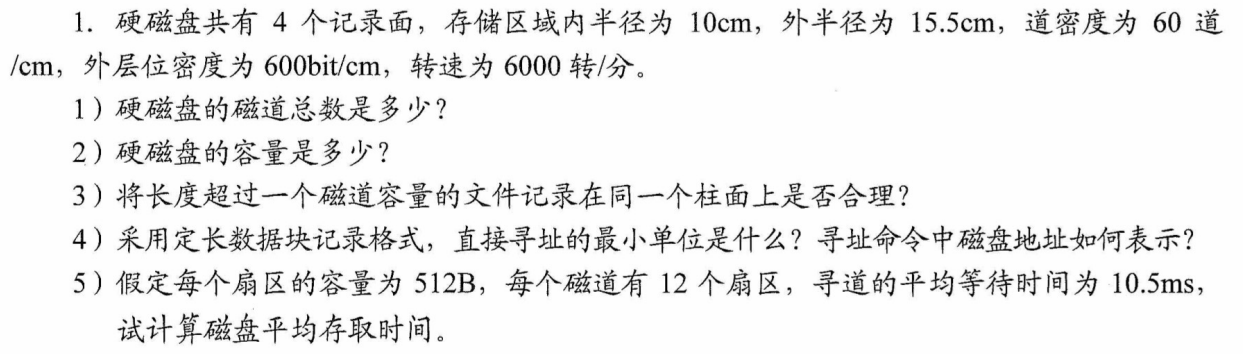

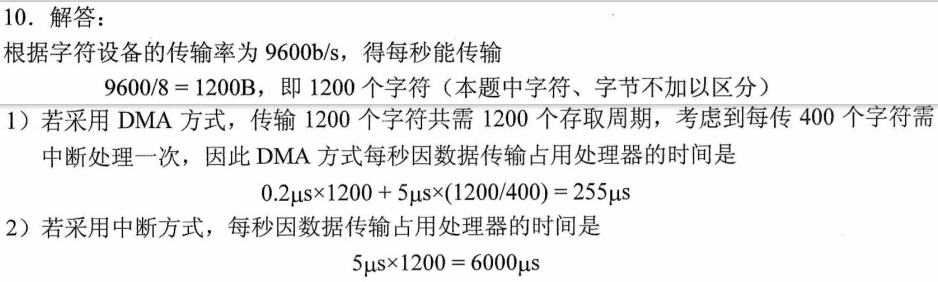

综合题

图片详情

解析

图片详情

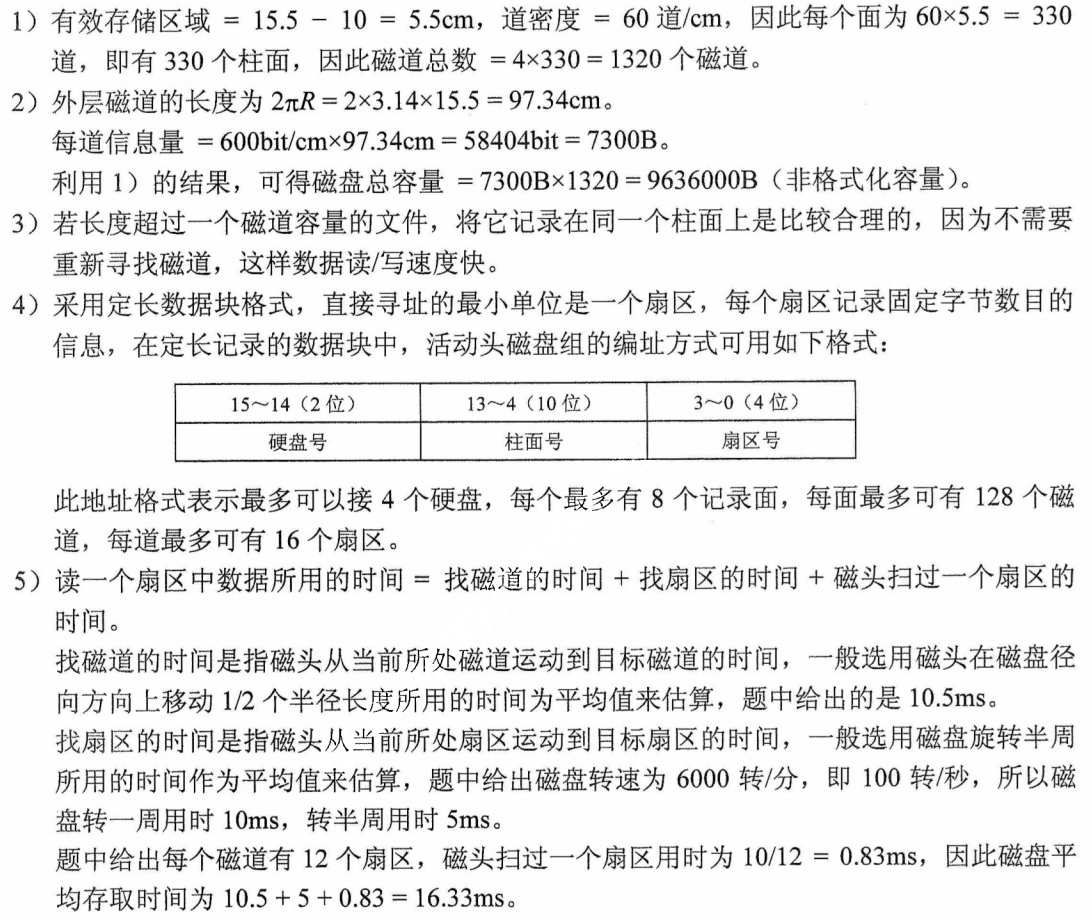

数据总线上传输的信息

图片详情

解析

图片详情

- I/O接口中的命令字

- I/O接口中的状态字

- 中断类型号

在统一编址的方式下,区分存储单元和IO设备是靠()。

A.不同的地址码

B.不同的地址线

C.不同的控制线

D.不同的数据线

解析

A

在统一编址的情况下,没有专门的I/O指令,因此用访存指令来实现I/O操作,区分存储单元和I/O设备是靠它们各自不同的地址码。

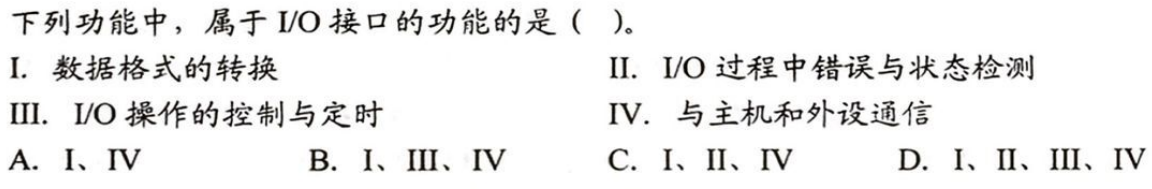

I/O接口的功能

图片详情

解析

图片详情

下列关于IO端口和接口的说法中,正确的是()。

A.按照不同的数据传送格式,可将接口分为同步传送接口和异步传送接口

B.在统一编址方式下,存储单元和IO设备是靠不同的地址线来区分的

C.在独立编址方式下,存储单元和IO设备是靠不同的地址线来区分的

D、在独立编址方式下,CPU需要设置专门的输入/输出指令访问端口

解析

D

选项D显然正确。按照不同的数据传送格式,可将接口分为并行接口和串行接口,因此A错;在统一编址方式下,存储单元和VO设备是靠不同的地址码而非地址线来区分的,因此 B错;在独立编址方式下,存储单元和UO设备是靠不同的指令来区分的,因此C错。

磁盘驱动器向盘片磁道记求数据时采用()方式写入。

B.串行

C.并行-串行

D.串行-并行

A.并行

解析

8.B

磁盘驱动器向盘片磁道记录数据时采用串行方式写入。

【2017统考真题】I/O指令实现的数据传送通常发生在().

A. I/O设备和I/O端口之间

B.通用寄存器和I/O设备之间

C. I/O端口和I/O端口之间

D.通用寄存器和I/O端口之间

解析

D

I/O端口是指I/O接口中用于缓冲信息的寄存器,由于主机和I/O设备的工作方式和工作速度有很大差异,I/O端口应运而生。在执行一条指令时,CPU使用地址总线选择所请求的I/O端口,使用数据总线在CPU寄存器和端口之间传输数据,所以选D。

【2009统考真题】下列选项中,能引起外部中断的事件是()。

A.键盘输入

B.除数为0

C.浮点运算下溢

D.访存缺页

解析

A

外部中断是指CPU 执行指令以外的事件产生的中断,通常指来自CPU 与内存以外的中断。A中键盘输入属于外部事件,每次键盘输入CPU都需要执行中断以读入输入数据,所以能引起外部中断。B中除数为0属于异常,也就是内中断,发生在CPU内部。C中浮点运算下溢将按机器零处理,不会产生中断。而D访存缺页属于CPU执行指令时产生的中断,也不属于外部中断。所以能产生外部中断的只能是输入设备键盘。

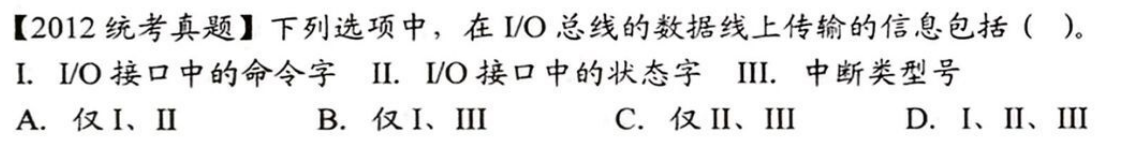

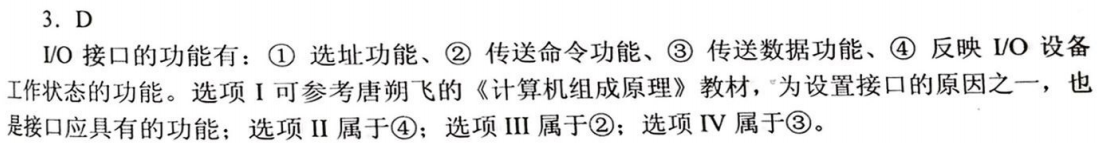

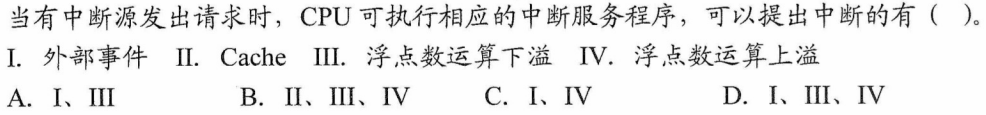

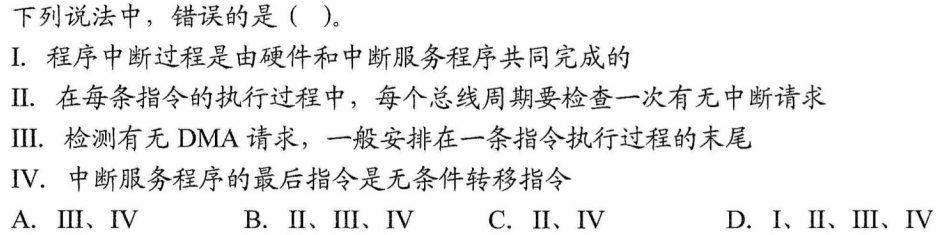

【2010统考真题】单级中断系统中,中断服务程序内的执行顺序是

图片详情

解析

图片详情

- 首先明确: $\color{green}{\text{关中断}}$ , $\color{green}{\text{保存断点}}$ , $\color{green}{\text{识别中断源}}$ 都是由硬件实现的

- 注意题目明说了是, $\color{green}{\text{单级中断系统}}$ ,所以不允许中断嵌套,也就是中断服务程序中不可能出现开中断,进入下一层中断

- 所以由,中断服务程序执行的内容为:保存现场,

【2014统考真题】若某设备中断请求的响应和处理时间为100ns,每 400ns发出一次中断请求,中断响应所允许的最长延迟时间为50ns,则在该设备持续工作过程中,CPU用于该设备的IO时间占整个CPU 时间的百分比至少是()。

A. 12.5%

B.25%

c.37.5%

D.50%

解析

5.B

每400ns 发出一次中断请求,而响应和处理时间为 100ns,其中容许的延迟为干扰信息,因为在50ns 内,无论怎么延迟,每400ns 仍要花费100ns 处理中断,所以该设备的IO时间占整个CPU时间的百分比为100ns/400ns = 25%。

- Q:为什么不是100/(400+100) = 20%

- A:每400ns发一次请求,证明cpu可以在400ns将请求处理掉,所以100ns是在400ns内的,参考文献

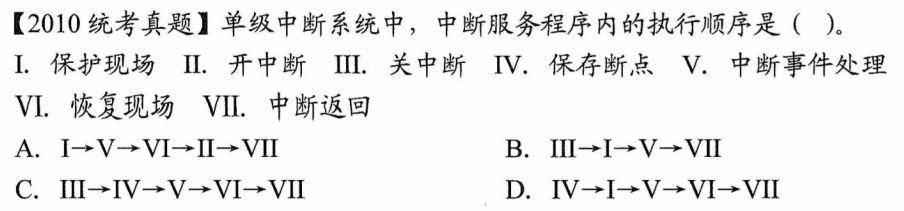

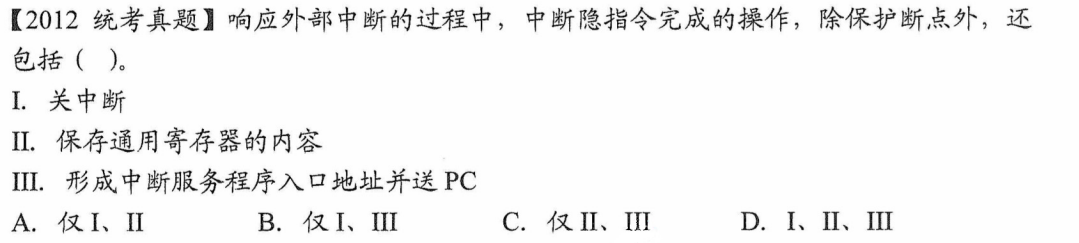

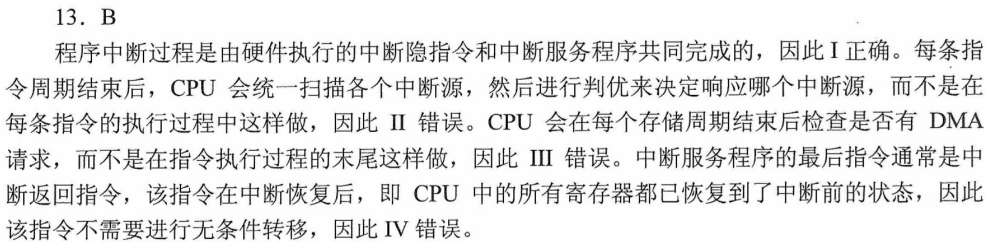

【2012统考真题】响应外部中断的过程中,中断隐指令完成的操作,除保护断点外,还包括()。

图片详情

解析

图片详情

- 保存通用寄存器的内容是在进入中断服务程序后首先进行的操作。

以下说法中,错误的是()。

A.中断服务程序一般是操作系统模块

B.中断向量方法可提高中断源的识别速度

C. 中断向量地址是中断服务程序的入口地址

D.重叠处理中断的现象称为中断嵌套

解析

C

中断服务程序是处理器处理的紧急事件,可理解为一种服务,是通过执行事先编好的某个特定的程序来完成的,一般属于操作系统的模块,以供调用执行,因此A 正确。中断向量由向量地址形成部件,即由硬件产生,并且不同的中断源对应不同的中断服务程序,因此通过该方法,可以较快速地识别中断源,因此B正确。中断向量是中断服务程序的入口地址, $\color{green}{\text{中断向量地址}}$ 是内存中存放中断向量的地址,即 $\color{green}{\text{中断服务程序入口地址的地址}}$ ,因此C错误。重叠处理中断的现象称为中断嵌套,因此D正确。

- 还记的操作系统的实验,中断服务程序确实是自己写的,编译到操作系统中去的

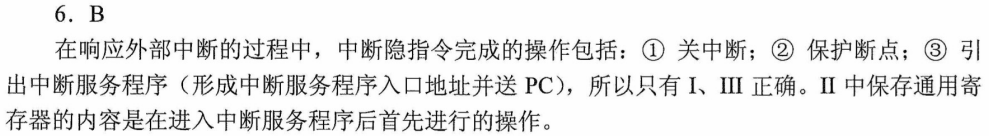

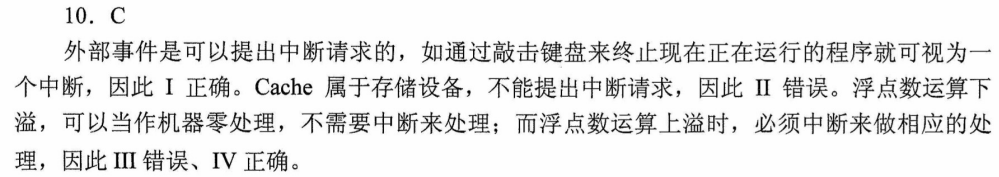

可以提出中断的情况,浮点数运算,cache,外部事件

图片详情

解析

图片详情

- 浮点数下溢可以当机器零处理

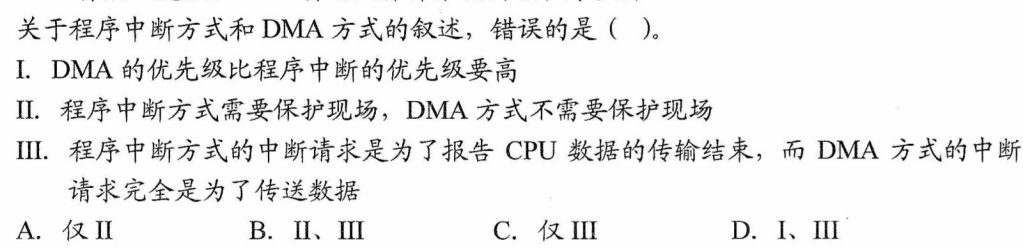

DMA与程序中断方式

图片详情

解析

图片详情

- $\color{red}{\text{注}}$ : $\color{green}{\text{DMA的优先级}}$ 比 $\color{green}{\text{程序中断的优先级}}$ 要 $\color{red}{\text{高}}$

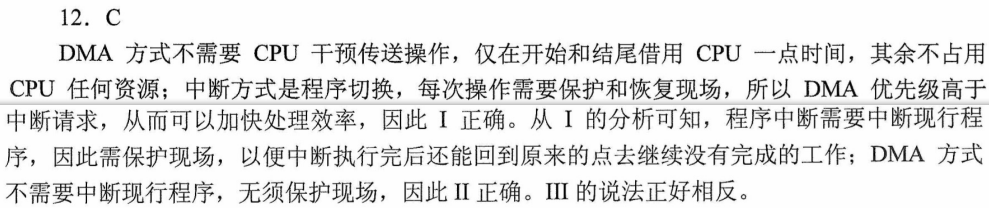

DMA与程序中断方式

图片详情

解析

图片详情

- $\color{green}{\text{执行过程的末尾}}$ ,不是每条 $\color{green}{\text{指令周期结束之后}}$

- 只是从新执行之前的程序,并不需要转移

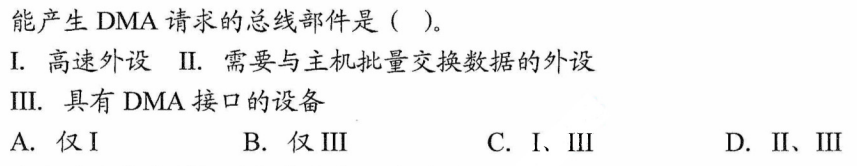

能产生 DMA请求的总线部件是

图片详情

解析

B

$\color{red}{\text{只有}}$ 具有DMA接口的设备才能产生DMA请求,即使当前设备是高速设备或需要与主机批量交换数据,若没有DMA接口的话,也不能产生 DMA请求。

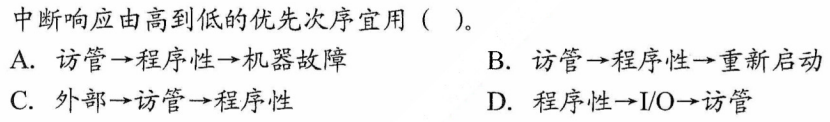

中断响应由高到低的优先次序宜用

图片详情

解析

B

中断优先级由高至低为访管→程序性→重新启动。重新启动应当等待其他任务完成后再进行,优先级最低,访管指令最紧迫,优先级最高。硬件故障优先级最高,访管指令优先级要高于外部中断。

在具有中断向量表的计算机中,中断向量地址是( )。

A.子程序入口地址

B.中断服务程序的入口地址

C.中断服务程序入口地址的地址

D.中断程序断点

解析

C

中断向量地址是中断向量表的地址,由于中断向量表保存着中断服务程序的入口地址,所以 $\color{green}{\text{中断向量地址}}$ 是 $\color{green}{\text{中断服务程序入口地址的地址}}$ 。

在配有通道的计算机系统中,用户程序需要输入/输出时,引起的中断是()。

A.访管中断

B.I/O中断

C.程序性中断

D.外中断

解析

A

用户程序需要输入/输出时,需要调用操作系统提供的接口(请求操作系统服务),此时会引起访管中断,系统由用户态转为核心态。

- $\blacktriangleright$(为什么不是I/O中断)

在中断周期中,由()将允许中断触发器置0。

A.关中断指令

B.中断隐指令

C.开中断指令

D.中断服务程序

解析

24.B

允许中断触发器置0表示关中断,由中断隐指令完成,即由硬件自动完成。

设置中断屏蔽标志可以改变()

A.多个中断源的中断请求优先级

B. CPU对多个中断请求响应的优先次序

C.多个中断服务程序开始执行的顺序

D.多个中断服务程序执行完的次序

解析

D

中断屏蔽标志的一种作用是实现中断升级,即改变中断处理的次序(注意分清中断响应次序和中断处理次序, $\color{green}{\text{中断响应}}$ 次序由 $\color{green}{\text{硬件排队电路}}$ 决定),因此其可以改变多个中断服务程序执行完的次序。

【2017统考真题】下列关于多重中断系统的叙述中,错误的是()。

A.在一条指令执行结束时响应中断

B.中断处理期间CPU处于关中断状态

C.中断请求的产生与当前指令的执行无关

D. CPU通过采样中断请求信号检测中断请求

解析

B

$\color{green}{\text{多重中断系统}}$ 在保护被中断进程现场时关中断,执行中断处理程序时开中断,选项B错误。CPU一般在一条指令执行结束的阶段采样中断请求信号,查看是否存在中断请求,然后决定是否响应中断,选项A、D正确。中断请求一般来自CPU 以外的事件,异常一般发生在CPU内部,选项C正确。

在CPU响应中断时,保护两个关键的硬件状态是()。

A. PC和IR

B.PC和PSW

C.AR和IR

D.AR和PSW

解析

B

程序计数器(PC)的内容是被中断程序尚未执行的第一条指令地址,程序状态字(PSW)寄存器保存各种状态信息。CPU响应中断后,需要保护中断的CPU现场,将PC和PSW压入堆栈,这样等到中断结束后,就可以将压入堆栈的原 $\color{green}{\text{PC}}$ 和 $\color{green}{\text{PSW}}$ 的内容恢复到相应的寄存器,原程序从断点开始继续执行。

在DMA传送方式中,由()发出 DMA请求,在传送期间总线控制权由()掌握。

A.外部设备、CPU

B.DMA控制器、DMA控制器

C.外部设备、DMA控制器

D.DMA控制器、内存

解析

C

在 DMA传送方式中,由外部设备向DMA控制器发出DMA请求信号,然后由DMA 控制器向CPU 发出总线请求信号。在 DMA方式中, $\color{red}{\text{DMA 控制器}}$ 在传送期间有 $\color{green}{\text{总线控制权}}$ ,这时CPU $\color{green}{\text{不能响应I/O中断}}$ 。

- $\mho$(那此时CPU除了运算,还可以干些什么呢)

下列叙述中,()是正确的。

A.程序中断方式和DMA方式中实现数据传送都需要中断请求

B.程序中断方式中有中断请求,DMA方式中没有中断请求

C.程序中断方式和DMA方式中都有中断请求,但目的不同

D. DMA要等指令周期结束时才可以进行周期窃取

解析

C

程序中断方式在数据传输时,首先要发出中断请求,此时CPU 中断正在进行的操作,转而进行数据传输,直到数据传送结束,CPU才返回中断前执行的操作。DMA方式只是在 DMA的前处理和后处理过程中需要用中断的方式请求CPU操作,但在数据传送过程中,并不需要中断请求,因此A错误。DMA方式和程序中断方式都有中断请求,但目的不同,程序中断方式的中断请求是为了进行数据传送,而DMA方式中的中断请求只是为了获得总线控制权或交回总线控制权,因此B错误、C正确。CPU对 DMA的响应可在指令执行过程中的 $\color{green}{\text{任何两个存取周期之间}}$ ,因此D错误。

【2013统考真题】下列关于中断IO方式和DMA方式比较的叙述中,错误的是( )。

A.中断I/O方式请求的是CPU处理时间,DMA方式请求的是总线使用权

B.中断响应发生在一条指令执行结束后,DMA响应发生在一个总线事务完成后

C.中断I/O方式下数据传送通过软件完成,DMA方式下数据传送由硬件完成

D.中断I/O方式适用于所有外部设备,DMA方式仅适用于快速外部设备

解析

D

中断处理方式:在IO设备输入每个数据的过程中,由于无须CPU干预,因而可使CPU与IO设备并行工作。仅当输完一个数据时,才需CPU花费极短的时间去做一些中断处理。因此中断申请使用的是CPU处理时间,发生的时间是在一条指令执行结束之后,数据在软件的控制下完成传送。而DMA方式与之不同。DMA方式:数据传输的基本单位是数据块,即在CPU与I/O 设备之间,每次传送至少一个数据块;DMA 方式每次申请的是总线的使用权,所传送的数据是从设备直接送入内存的,或者相反;仅在传送一个或多个数据块的开始和结束时,才需要CPU干预,整块数据的传送是在控制器的控制下完成的。

- B选项参见上一题:存取事件可以理解为一个总线事务

- D选项应该是有DMA控制器的设备都可以

关于中断和DMA,下列说法中正确的是()。

A. DMA请求和中断请求同时发生时,响应DMA请求

B. DMA请求、非屏蔽中断、可屏蔽中断都要在当前指令结束之后才能被响应

C.非屏蔽中断请求优先级最高,可屏蔽中断请求优先级最低

D.若不开中断,所有中断请求就不能响应

解析

A

DMA请求的优先级高于中断请求,以防止高速设备数据丢失,因此选项A正确。中断必须在CPU执行指令结束时才可被响应,而 DMA请求在每个 $\color{green}{\text{机器周期}}$ 结束后应可被响应,因此选项B错误。 $\color{green}{\text{DMA 的优先级}}$ 要比外中断(非屏蔽中断、可屏蔽中断)高,因此C错误。内中断是不可被屏蔽的,因此即使不开中断,仍可响应 $\color{green}{\text{内中断}}$ ,因此选项D错误。

在主机和外设的信息传送中,()不是一种程序控制方式。

A.直接程序传送

B.程序中断

C.直接存储器存取(DMA)

D.通道控制

解析

C

只有DMA方式是靠硬件电路实现的,三种基本的程序控制方式即直接程序传送、程序中断、通道控制都需要程序的干预。

- $\color{red}{\text{通道}}$ 是一种 $\color{green}{\text{程序控制方式}}$

在DMA方式传送数据的过程中,由于没有破坏()的内容,所有CPU可以正常工作(访存除外)。

A.程序计数器

B.程序计数器和寄存器

C.指令寄存器

D.堆栈寄存器

解析

39.B

DMA方式传送数据时,挪用周期不会改变CPU现场,因此无须占用CPU的程序计数器和寄存器。

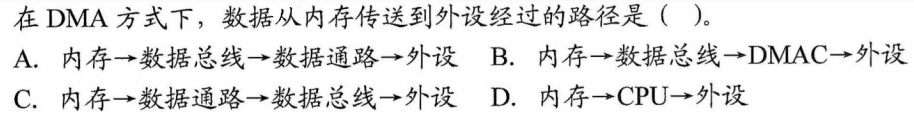

在DMA 方式下,数据从内存传送到外设经过的路径是

图片详情

解析

40.B

DMA方式不经过CPU,输出从内存经过数据总线,传送到 DMA 控制器的 DMAC 中,再传送给外设。类似这样的传输路径称为数据通路。

【2015统考真题】在采用中断IO方式控制打印输出的情况下,CPU和打印控制接口中的IO端口之间交换的信息不可能是()。

A.打印字符

B.主存地址

C.设备状态

D.控制命令

解析

41.B

在程序中断IO 方式中,CPU和打印机直接交换,打印字符直接传输到打印机的I/O端口,不会涉及主存地址。而CPU和打印机通过I/O端口中的状态口和控制口来实现交互。

【2019统考真题】某设备以中断方式与CPU进行数据交换,CPU主频为1GHz,设备接口中的数据缓冲寄存器为32位,设备的数据传输率为50kB/s。若每次中断开销(包括中断响应和中断处理)为1000个时钟周期,则CPU用于该设备输入/输出的时间占整个CPU时间的百分比最多是()。

A. 1.25%

B. 2.5%

C. 5%

D.12.5%

解析

A

设备接口中的数据缓冲寄存器为32位,即一次中断可以传输4B数据,设备数据传输率为50kB/s,共需要12.5k 次中断,每次中断开销为1000 个时钟周期,CPU主频为1GHz,则CPU用于该设备输入/输出的时间占整个CPU时间的百分比最多是(12.5k×1000)/1G= 1.25%。

- $\color{green}{\text{数据缓冲寄存器}}$ :一次中断可以传输的数据大小

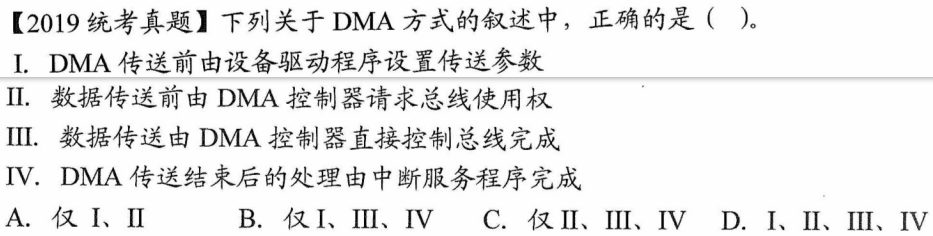

2019年真题,DMA

图片详情

解析

D

每类设备都配置一个设备驱动程序,设备驱动程序向上层用户程序提供一组标准接口,负责实现对设备发出各种具体操作指令,用户程序不能直接和 DMA 打交道。DMA 的数据传送过程分为预处理、数据传送和后处理3个阶段。预处理阶段由CPU完成必要的准备工作,数据传送前由DMA控制器请求总线使用权;数据传送由DMA控制器直接控制总线完成;传送结束后,DMA控制器向CPU发送中断请求,CPU执行中断服务程序做DMA结束处理。

【2020统考真题】下列关于“自陷”( Trap,也称陷阱)的叙述中,错误的是()。

A.自陷是通过陷阱指令预先设定的一类外部中断事件

B.自陷可用于实现程序调试时的断点设置和单步跟踪

C.自陷发生后CPU将转去执行操作系统内核相应程序

D.自陷处理完成后返回到陷阱指令的下一条指令执行

解析

A

本题更是操作系统的考点。自陷是一种内部异常,A错误。在80x86 中,用于程序调试的“断点设置”功能是通过“自陷”方式实现的,B正确。执行到自陷指令时,无条件或有条件地自动调出操作系统内核程序进行执行,C正确。CPU执行“陷阱指令”后,会自动地根据不同“陷阱”类型进行相应的处理,然后返回到“陷阱指令”的下一条指令执行,D正确。

【2020统考真题】若设备采用周期挪用DMA 方式进行输入和输出,每次DMA传送的数据块大小为512字节,相应的IO接口中有一个32位数数据缓冲寄存器。对于数据输入过程,下列叙述中,错误的是()。

A.每准备好32位数据,DMA控制器就发出一次总线请求

B.相对于CPU,DMA控制器的总线使用权的优先级更高

C.在整个数据块的传送过程中,CPU不可以访问主存储器

D.数据块传送结束时,会产生“DMA传送结束”中断请求

解析

C

$\color{green}{\text{周期挪用法}}$ 由DMA控制器挪用一个或几个主存周期来访问主存,传送完一个数据字后立即释放总线,是一种单字传送方式, $\color{green}{\text{每个字传送完}}$ 后 $\color{green}{\text{CPU可以访问主存}}$ ,选项C错误。 $\color{green}{\text{停止 CPU访存法}}$ 则是指在整个数据块的传送过程中,使CPU脱离总线, $\color{green}{\text{停止}}$ 访问主存。

在 DMA 方式下,主存和IO设备之间有一条物理通路相连吗?

解析

没有。通常所说的 DMA方式在主存和IO设备之间建立一条“直接的数据通路”,使得数据在主存和IO设备之间直接进行传送,其含义并不是在主存和IO之间建立一条物理直接通路,而是主存和IO设备通过 $\color{green}{\text{IO设备接口}}$ 、 $\color{green}{\text{系统总线}}$ 及 $\color{green}{\text{总线桥接部件}}$ 等相连,建立一个信息可以相互通达的通路,这在逻辑上可视为直接相连的。其 $\color{green}{\text{“直接”}}$ 是相对于要通过CPU才能和主存相连这种方式而言的。

回答下列问题:

1)一个完整的指令周期包括哪些CPU工作周期?

2)中断周期前和中断周期后各是CPU的什么工作周期?

3)DMA周期前和DMA周期后各是CPU的什么工作周期?

解析

1)一个完整的指令周期包括取指周期、间址周期、执行周期和中断周期。其中取指周期和执行周期是每条指令均有的。

2)中断周期前是执行周期,中断周期后是下一条指令的取指周期。

3)DMA周期前可以是取指周期、间址周期、执行周期或中断周期,DMA周期后也可以是取指周期、间址周期、执行周期或中断周期。总之,DMA周期前后都是机器周期。

假定某IO设备向CPU传送信息的最高频率为4万次/秒,而相应中断处理程序的执行时间为40 $\mu$ s,则该I/O设备是否可采用中断方式工作?为什么?

解析

IO设备传送一个数据的时间为1/(4× $10^4$ )s = 25 $\mu$ s,所以请求中断的周期为25$\mu$s,而相应中断处理程序的执行时间为40$\mu$s,大于请求中断的周期,会丢失数据(单位时间内TO请求数量比中断处理的多,自然会丢失数据),所以不能采用中断方式。

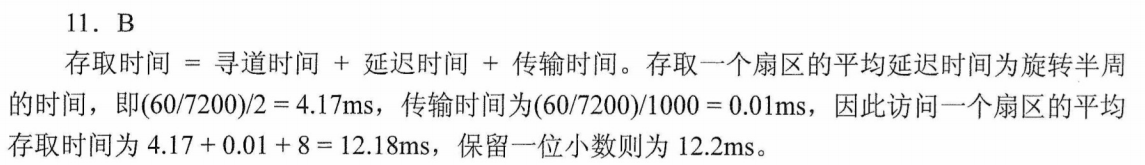

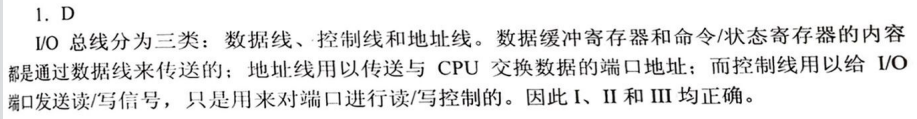

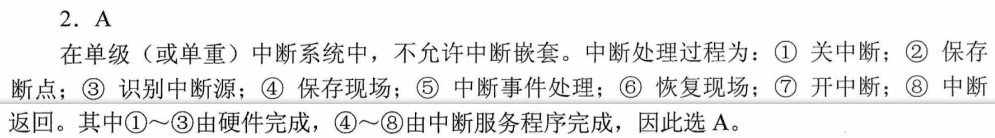

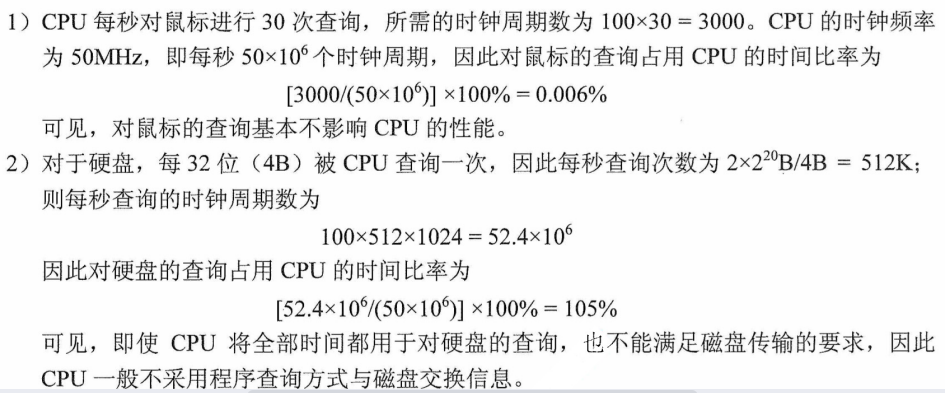

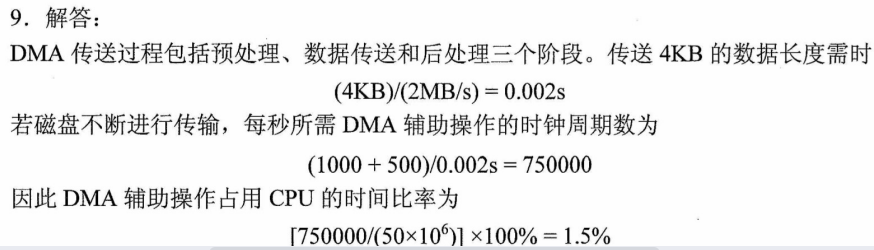

在程序查询方式的输入/输出系统中,假设不考虑处理时间,每个查询操作需要100 个时钟周期,CPU的时钟频率为50MHz。现有鼠标和硬盘两个设备,而且CPU必须每秒对鼠标进行30次查询,硬盘以32位字长为单位传输数据,即每32位被CPU查询一次,传输率为2× $2^{20}$ B/s。求CPU对这两个设备查询所花费的时间比率,由此可得出什么结论?

解析

图片详情

- 硬盘一般不适用程序查询的方式

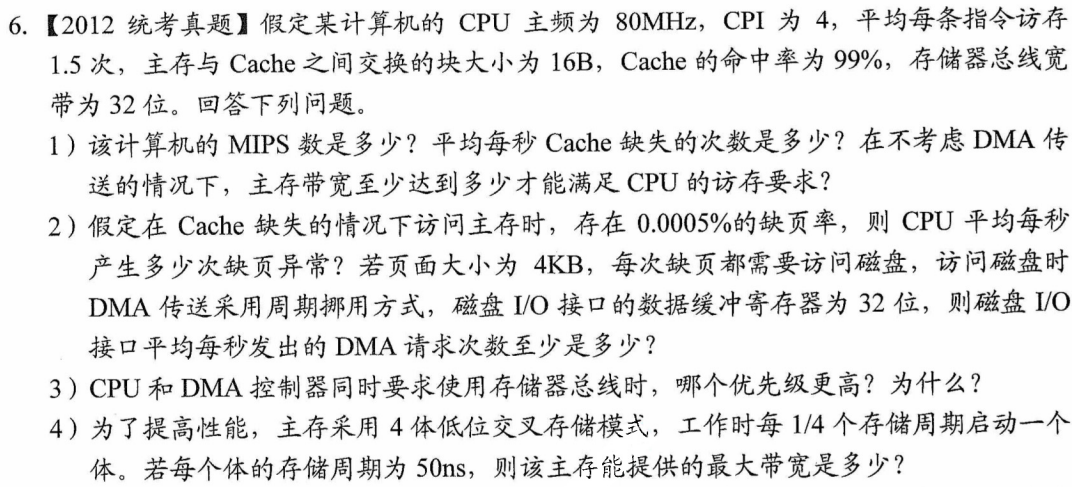

2012年真题,计算机的性能指标、存储器的性能指标、DMA 的性能分析、DMA方式的特点及多体交叉存储器的性能分析

图片详情

解析

图片详情

- cpu 和 cache 和 主存,而cache与主存之间交换数据的单位是块,且只有cache确实的时候才需要访存

- 为什么不是用存储器总线的位数,这里的存储器指的是磁盘

- 注意进位: 0.3 $\times \dfrac{0.0005}{100}$ = 1.5

- 最后一题,这里求的是理论带宽,不是离散次的情况

- 离散次的求法:$\dfrac{4}{40 ns = 40 ns} \times 4B$

- 这里的进位单位是1000,$\mho$(怎么确定进位单位)

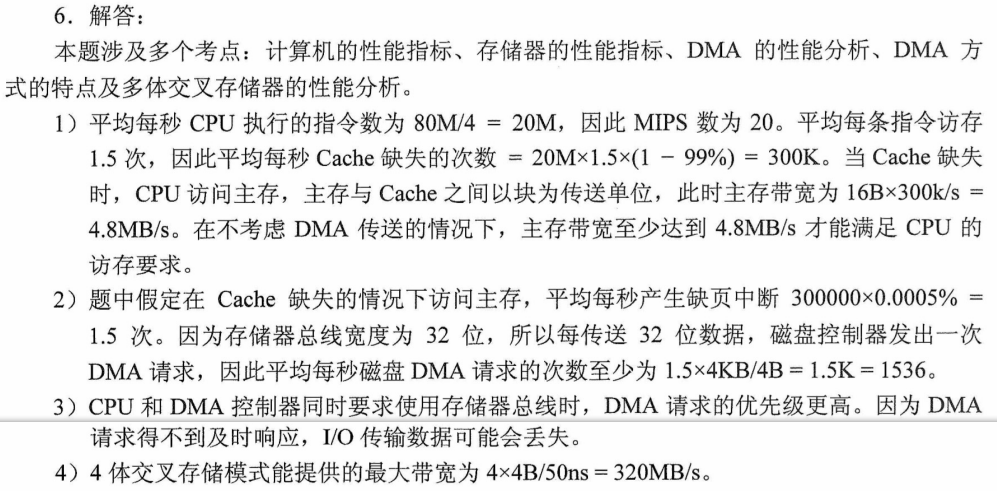

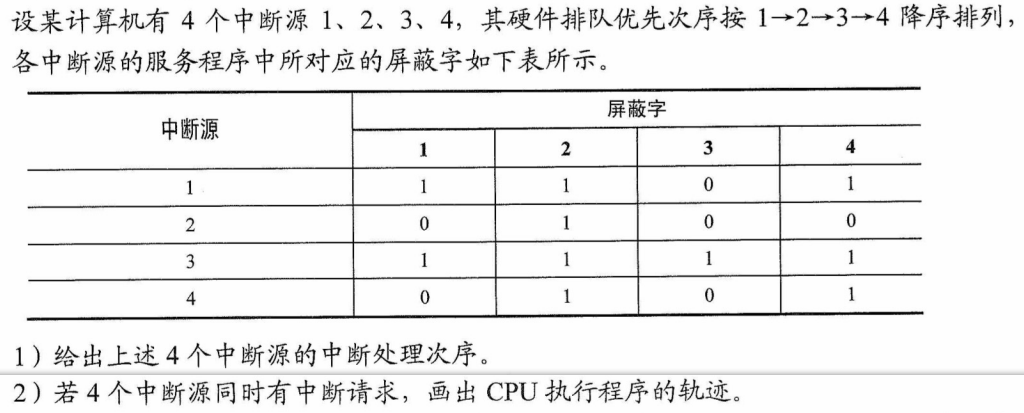

2016年真题,异步串行通信

图片详情

解析

图片详情

- 有一个起始位,题目没有给出

- Q:为什么都是只用 $\color{green}{\text{+ 10}}$ 的响应周期

- A:看起来好像是需要 $\color{green}{\text{+ 20}}$ (前面的10和后面的10),但实际上,后面的10是不用算的,他是下一个请求的开始

- Q:为什么CPU是20 $\times$ 4 ,但是一个字符的传送时间是 15 $\times$ 4

- A:因为传送的时间中,后面的时间用被算在了0.5ms里面

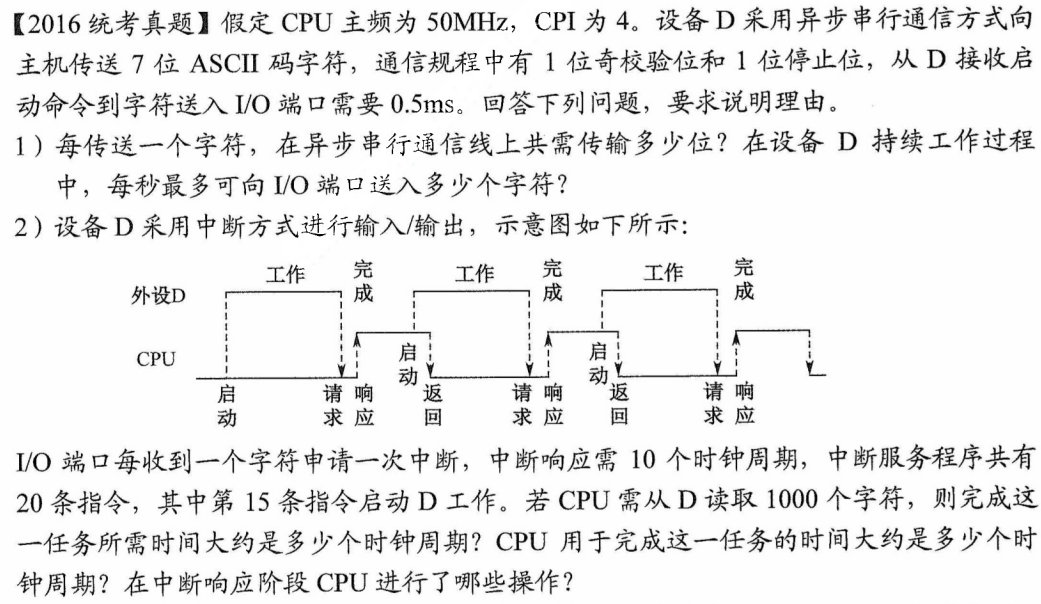

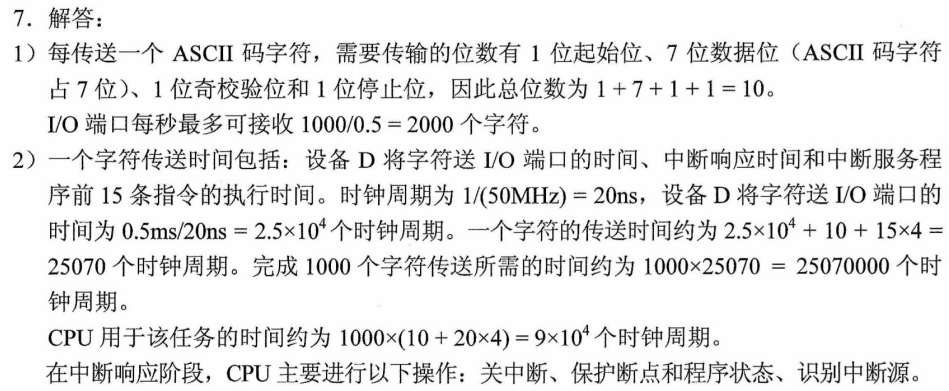

执行程序的轨迹与中断屏蔽字

图片详情

解析

图片详情

- 次序肯定能求对的

- 稍微瞄一下所谓的「执行程序的轨迹」怎么画就好了

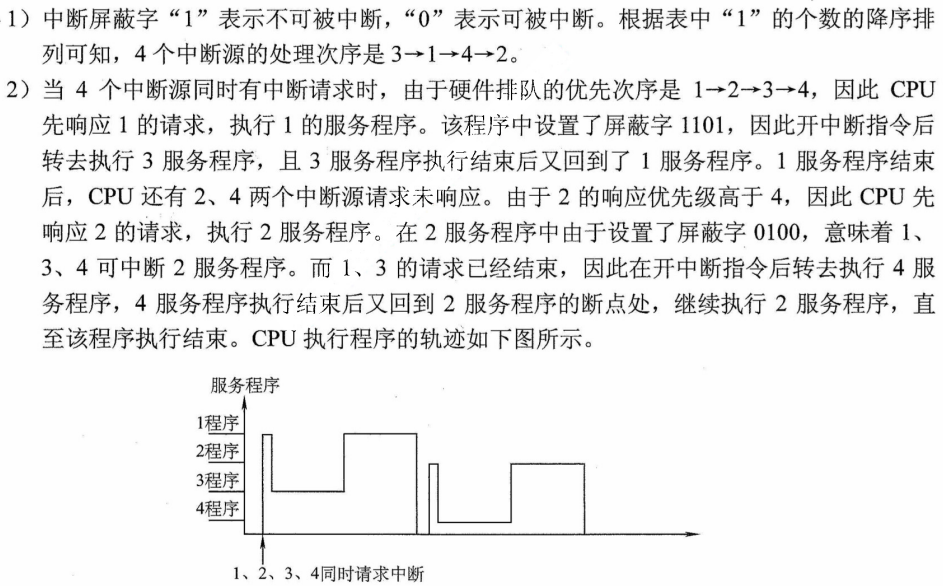

假设磁盘采用DMA方式与主机交换信息,其传输速率为2MB/s,而且 DMA的预处理需要1000个时钟周期,DMA完成传输后处理中断需要500个时钟周期。若平均传输的数据长度为4KB,试问在硬盘工作时,50MHz的处理器需用多大的时间比率进行DMA辅助操作(预处理和后处理)?

解析

图片详情

$\color{red}{\text{DMA传送过程}}$ 包括 $\color{green}{\text{预处理}}$ 、 $\color{green}{\text{数据传送}}$ 和 $\color{green}{\text{后处理}}$ 三个阶段。

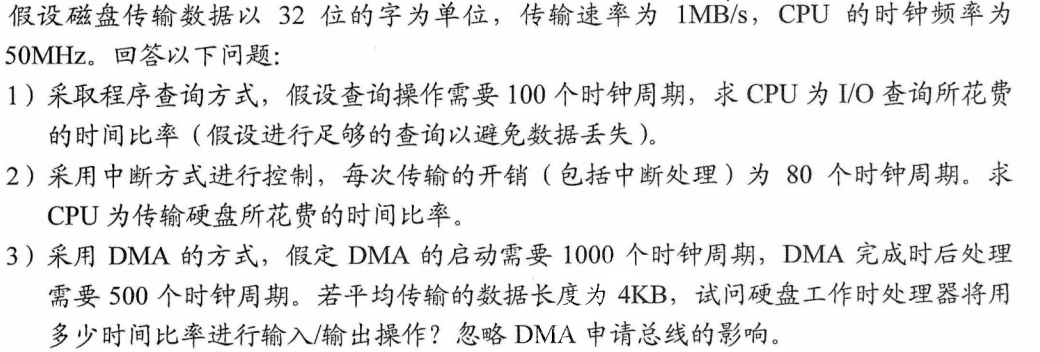

一个 DMA接口可采用周期窃取方式把字符传送到存储器,它支持的最大批量为400B。若存取周期为0.2 $\mu$ s,每处理一次中断需5 $\mu$ s,现有的字符设备的传输率为9600b/s。假设字符之间的传输是无间隙的,试问DMA方式每秒因数据传输占用处理器多少时间?若完全采用中断方式,又需占处理器多少时间(忽略预处理所需时间)?

解析

图片详情

- Q:存储周期对结果的影响是什么

- A:一个存储周期,就是传送一个字符的时间

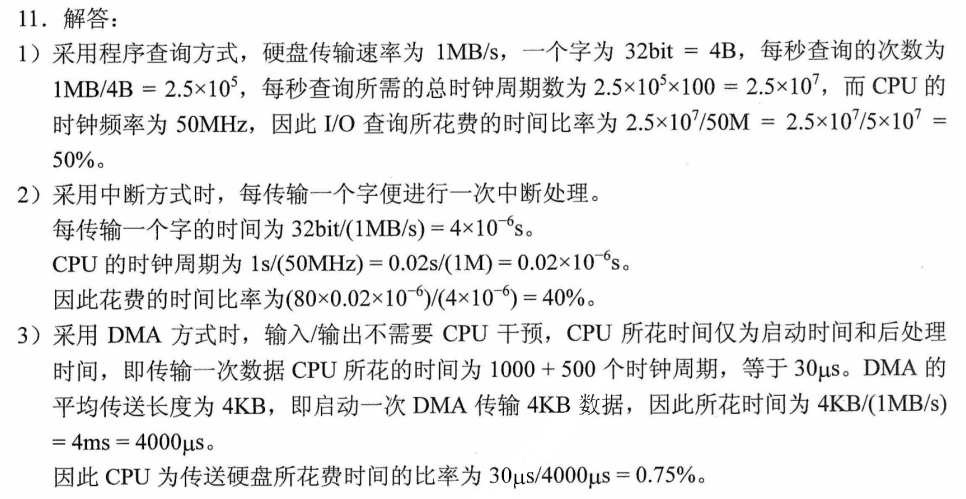

自编题

图片详情

解析

图片详情

- 第二题,应该是第一题的4/5

【2018统考真题】假定计算机的主频为500MHz,CPI为4。现有设备A和B,其数据传输率分别为2MB/s 和40MB/s,对应IO接口中各有一个32位数据缓冲寄存器。回答下列问题,要求给出计算过程。

1)若设备A采用定时查询I/O方式,每次输入/输出都至少执行10条指令。设备A最多间隔多长时间查询一次才能不丢失数据?CPU 用于设备A 输入/输出的时间占CPU总时间的百分比至少是多少?

2)在中断IO方式下,若每次中断响应和中断处理的总时钟周期数至少为400,则设备B能否采用中断IO方式?为什么?

3)若设备B采用 DMA 方式,每次 DMA传送的数据块大小为1000B,CPU用于DMA预处理和后处理的总时钟周期数为500,则CPU用于设备B输入/输出的时间占CPU总时间的百分比最多是多少?

解析

- 第一题和最后一道题皆能做对

- 第二题我算出来是50个时钟周期,否则数据会丢失